ニュース情報

ニュース情報 知識コラム

知識コラムチップスタック技術はもうよく知られていると思いますが、ファーウェイが新旗艦携帯電話mate 60シリーズを発表し、採用したキリン9000 sチップは、チップスタック技術を使用しており、7 nmのプロセスプロセスでクアルコムやアップルの4 nmプロセスのチップと戦ってきたことで、チップスタック技術はたちまち話題になっています。

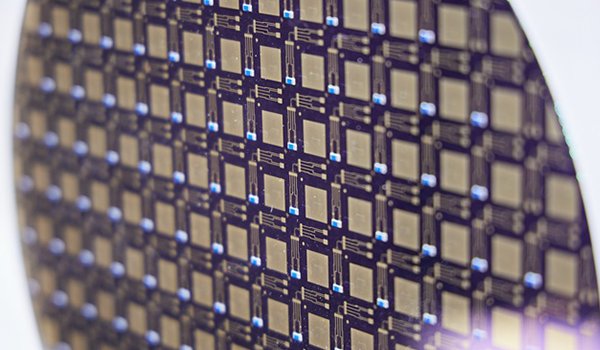

過去数十年間、ムーア法則の影響が徐々に弱まるにつれて、半導体業界は従来の平面トランジスタを超える代替ソリューションを探してきた。このような背景の下で、チップスタック技術は画期的な進歩となり、集積回路の発展に新たな希望をもたらした。本文はチップスタック技術の原理、優勢及び将来のチップ設計に対する影響を深く検討する。

チップスタック技術の解析:

垂直集積方式を用いて複数のチップを積層し、層と層との電気的接続をシリコン貫通孔(TSV、Through−Silicon Vias)またはその他の相互接続技術により実現する3次元IC技術とも呼ばれるチップ積層技術。従来の2 D平面レイアウトに比べて、スタックチップは、より短い信号経路、より高い動作速度、およびより低い消費電力を提供することができる。

チップスタック技術の技術的優位性:

より小さいサイズ:垂直統合により占有スペースを削減し、デバイスをより軽量化します。

高性能と低消費電力:チップ間の信号伝送距離を減少させ、速度を高めると同時にエネルギー消費量を減少させる。

柔軟な設計:異なるプロセスのチップを組み合わせてスタックし、優位性の相補性を実現することができる。

チップスタック技術の応用の将来性:

チップスタック技術は、AIチップ、高性能コンピューティング、メモリ、モバイルデバイスを含むが、これらに限定されない多くの分野で広く応用される見通しがある。また、ネットワークサーバ、カーエレクトロニクス、宇宙航空などの分野でも重要な価値を示している。

拡張読書:チップスタック技術はどのように動作しますか?

チップスタックは複雑な製造プロセスに関連している。まず、標準的なチップを製造し、その表面または内部に微小な貫通孔を製造する必要がある。完成したら、これらのチップを正確にアラインメントして積層し、金属を用いてこれらの貫通孔を充填して電気的接続を形成する。これには、極めて高精度なアライメント技術と、精密な材料工学が必要です。

チップスタック製造の課題

熱管理:チップの積み重ねに伴い、熱の排出が重要な問題となっている。

相互接続技術:より効率的で信頼性の高い接続技術を開発して、より多くの入出力インタフェースを処理する必要があります。

テストと検証:スタックされたチップの方がテストが難しく、チップの信頼性を保証するための新しい戦略が必要です。

チップスタックとムーアの法則

従来、チップ性能の向上はトランジスタサイズの縮小、すなわちモル法則に依存していた。しかし、物理的限界が近づくにつれて、トランジスタのスケーリングはますます困難になってきた。チップスタック技術は集積回路の性能を向上させ続けるために新しい次元を提供し、ある専門家はこれがムーア法則の自然な延長だと考えている。

要するに、チップスタック技術は次世代半導体の発展を推進する重要な技術の一つである。電子機器の性能向上を推進するだけでなく、デザイナーにより大きな設計スペースを提供し、よりコンパクトで効率的な電子製品設計を実現することができます。浮思特科技は新エネルギー自動車、電力新エネルギー、家庭電器、タッチディスプレイに専念し、4つの分野で、顧客に方案開発からチップ選択型購入までのワンストップサービスを提供し、核心技術を持つ電子部品サプライヤーとソリューション商である。