新闻资讯

新闻资讯 知识专栏

知识专栏在许多功率转换应用中,碳化硅比硅显示出显着的性能优势。更广泛的采用取决于进一步降低成本和批量生产,以满足全球电气化程度不断提高对功率半导体的强劲预测需求。在本文中,我们将讨论 工程 SIC 衬底的潜在优势。

智能碳化硅工艺

Soitec 在 20 世纪 90 年代初开发了 Smart Cut 工艺。这涉及使用“处理”晶圆和“施主”晶圆。氧化的供体晶片在氧化物表面下方的给定深度处注入氢气,然后翻转到处理晶片上。首先使用一系列退火在注入深度处分割施主晶圆,然后将施主晶圆的薄片熔合到处理晶圆上。顶面经过抛光,可用于设备制作。由此产生的氧化硅晶圆在射频、低功耗逻辑和电源 IC的制造方面具有多种优势:氧化物提供隔离,可以更轻松地集成不同电压等级的器件,具有闩锁、降低结电容和更低泄漏的优点。经过一些准备后,供体晶圆可以重复使用。SmartSiC 工艺已采用此基本流程,但存在一些关键差异。在这种情况下,处理晶圆是高掺杂多晶硅 (pSiC) 晶圆,并使用导电键合将其熔合到施主晶圆,施主晶圆通常是生产级单晶 4H SiC 晶圆。供体晶圆的碳面向下键合,确保顶面是硅面,就像传统的SiC衬底一样。该 SiC 层的厚度约为 1 µm 或更小,是可在其上生长器件外延层的种子层。

智能碳化硅特性

让我们来看看 SmartSiC 生产的器件的一些特性以及该衬底可为 SiC 功率器件的制造流程和性能带来的潜在优势。

降低CO2足迹

生产单晶 SiC 基板的标准工艺非常耗能。物理气相传输 (PVT) 升华工艺需要高温 (>2,000 ° C)。相比之下,pSiC 可以通过较低温度、高通量的化学气相沉积生产。Soitec 概述的 SmartSiC 流程显示标准单晶供体晶片可重复使用 10 次。其生命周期分析估计显示,在目前的发电结构下,与标准流程相比,SmartSiC 流程可减少 4 倍的二氧化碳排放量。

更低的基材电阻

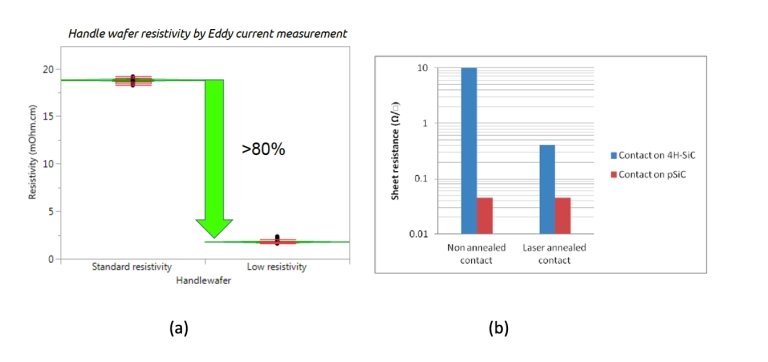

在垂直SiC MOSFET器件中,净器件电阻主要由横向反转沟道电阻、栅极下方电流流动时的JFET电阻、通过外延层的漂移电阻和衬底电阻相加而成。标准基板的厚度通常从 350 µm 开始,在背面接触金属化之前减薄至 100 µm 至 200 µm 之间。市售生产级 4H-SiC 基板的方块电阻通常在 15–20 mΩ-cm 范围内。这种掺杂水平受到 PVT 生长过程中与晶体质量之间的权衡的限制。相比之下,SmartSiC 中使用的 pSiC 衬底可以掺杂得更高,典型值为 2 mΩ-cm。基板电阻的相对贡献取决于几个因素,包括设备的电压等级。例如,与 1,200V MOSFET 相比,具有较薄外延(漂移)层的 750V MOSFET 对衬底电阻的贡献百分比更大,其中较厚的漂移层对电阻的贡献相对较大。基材。在 750VMOSFET 的衬底可贡献器件总通态电阻 (R DS(on) ) 的 15% 以上。

通过更简单的工艺流程降低背面接触电阻

标准 SiC 工艺流程中的背接触通常通过激光退火形成硅化镍层。Soitec 已证明,即使无需激光退火,pSiC 基板的背面薄层电阻也比标准流程低 10 倍。

图1

图 1 描述了 SmartSiC 流程对基板和背面接触电阻的改善。

改善晶圆平整度和翘曲度

与标准 SiC 衬底相比,pSiC 衬底已被证明具有改进的平坦度(通过位点平坦度最小二乘范围测量),并且当晶圆经过背面研磨工艺时,翘曲度减少了 2 倍以上。

缺陷和检查

Soitec 已证明,在 SmartSiC 上 KOH 蚀刻后拍摄的缺陷密度图像与供体晶圆的缺陷密度图像相同。此外,SmartSiC 晶圆被证明与 SICA 等标准光学检测工具兼容。顶部的薄种子层使 SiC 能够看到 pSiC 基底表面。

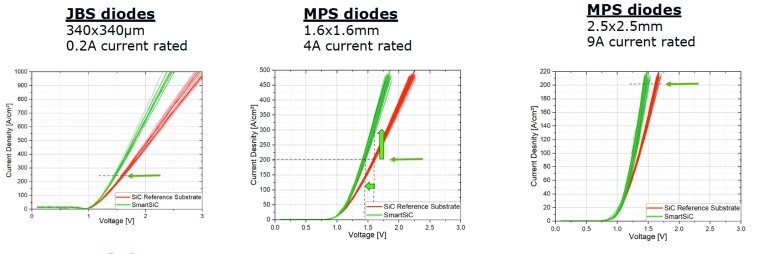

改善器件特定电阻

改进的衬底和背面接触电阻直接转化为改进的器件品质因数。例如,在我们上面讨论的 750V SiC MOSFET 示例中,器件比电阻的改进可高达 20%。图 2 显示了比较肖特基二极管的正向 IV 特性的数据。可以看到正向阻力显着降低 (>10%)。这种性能提升大约相当于设备一代的飞跃所带来的提升。

图2

更小的模具和更高的产量

对于给定的器件额定值,可以利用更高的电流密度来使芯片变得更小,从而以更高的产量提供每晶圆更多芯片的复合优势。这可以直接转化为成本改进。

可靠性

对基于标准单晶 SiC 的肖特基二极管与 SmartSiC 晶圆构建的肖特基二极管进行了有源功率循环测试 (PCT)。这些 5 × 10 毫米芯片的标准 SiC 典型额定电流为 138 A,SmartSiC 典型额定电流为 146 A。背面采用银烧结,顶部触点采用铝线接合。PCT 的目的是使温度升高 80 K 和 120 K,循环经过三秒的加热阶段,然后是六秒的冷却阶段。超过 300 千周期的测试证实了带有银烧结芯片连接的 SmartSiC 的卓越性能。寿命延长了 2 倍,温度波动能力提高了 20 K。

这项研究展示了 SmartSiC 键合界面的可靠性。器件级的其他可靠性研究,例如 MOSFET 体二极管稳定性、需要短路承受时间和反向偏压应力(如 HTRB 和 HTGB)才能获得对该技术的进一步信心。分立和模块级别的特定应用功率转换压力测试也将是大规模使用该技术的重要前提。

浮思特科技深耕功率器件领域,为客户提供IGBT、IPM模块等功率器件以及MCU和触控芯片,是一家拥有核心技术的电子元器件供应商和解决方案商。