新闻资讯

新闻资讯 知识专栏

知识专栏 光刻成本的上升、特征尺寸的缩小以及需要替代铜的材料,这些因素共同推动了对区域选择性沉积(ASD)技术的新兴趣。ASD是原子层沉积的延伸,旨在从底层构建电路特征,而如何绕过光刻技术制造芯片。

目前看来,光刻仍将是一种关键工具。但长期以来,它一直是半导体制造中最昂贵的工艺,并且随着极紫外光刻(EUV)的出现,成本变得更高。在未来的几代设备中,即使是EUV工具也需要多次曝光才能达到所需的特征尺寸。边缘位置误差正在占据总误差预算的越来越大比例。将新层对准现有特征可以消除光刻步骤并减少边缘位置误差的影响。

特征尺寸的缩小也推动了对钌互连的兴趣,这可能是自铜引入以来互连堆栈的最大变化。当线宽低于100纳米时,由于界面散射,铜的电阻率开始增加,而其他金属可能表现更好。与铜不同,钌扩散相对缓慢,因此不需要阻挡层。结果是,基于相同设计规则的钌线的实际尺寸比铜线更大。

与此同时,使光刻更困难的趋势也使得原子层沉积(ALD)更具成本效益。更薄的层使得ALD的低沉积速率不再成为问题。

想要钌沉积在需要的位置,而不是不需要的位置

区域选择性沉积是一个涵盖多种不同工艺方案的总称,包括模板生长和地形选择性。最近的研究主要集中在从预先存在的设备图案中获得选择性的工艺。例如,韩国汉阳大学的李正民和金宇熙发现,他们的Ru(TMM)(Co)3前驱体在二氧化硅上的成核速率高,但在氮化钛上的成核速率低。因此,钌结构可以自对准填充氧化物沟槽。

然而,这种内在的表面选择性并不够。随着沉积的进行,材料仍会在非生长表面累积。一旦覆盖了这些表面,选择性就会丧失。ASD的关键挑战在于找到足够有选择性的工艺,并在沉积所需的膜厚时保持足够的选择性。

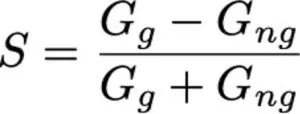

更准确地说,选择性定义为:

Gg和Gng分别是目标区域和非目标区域的生长速率。可以通过额外的表面处理来促进目标区域的沉积,抑制非目标区域的沉积,或者两者兼而有之。

最简单的ASD方法之一依赖自组装单分子层(SAMs)来对前驱体气体形成物理屏障。自组装单分子层使用一端带有官能团的单体。这个官能团被设计成附着在非目标区域。

SAMs非常多功能,可以设计成附着在几乎任何表面上,但在半导体制造中难以应用。通常需要将晶圆浸入单体溶液中,再等待沉积的分子自行排列。这一过程可能需要几个小时到整整一天。即便如此,涂层中仍常见针孔和其他缺陷。尽管存在气相SAMs,但无论是气相还是溶液型分子,其本质上都相当大,通常在2到3纳米。随着特征尺寸的缩小,将它们嵌入小沟槽并留出沉积薄膜的空间变得更加困难。

SAMs的局限性促使人们研究小分子抑制剂。这些抑制剂通常通过化学钝化非生长表面来工作。然而,正如斯坦福大学化学工程教授Stacey Bent在今年的材料研究学会(MRS)春季会议上的演讲中指出的那样,抑制剂分子的形状和取向仍然很重要。例如,吡啶对于钌沉积并不是很好的抑制剂,而吡咯和苯胺等其他含氮芳香族化合物则非常有效。根据Bent的密度泛函理论(DFT)计算,吡啶似乎以直立姿态绑定到表面,而另外两个则是平面结构。抑制剂与前驱体之间的反应和互溶性也起作用。例如,Bent说,甲磺酸是从DMAI(异丙氧基二甲基铝)在铜上沉积铝的良好抑制剂,但对于其他金属或前驱体则不是这样。

抑制剂的阻挡能力还取决于它在表面覆盖的程度。上述汉阳大学的研究使用(N,N-二乙氨基)三甲基硅烷(DEATMS)作为钌沉积的抑制剂。研究人员发现,DEATMS分子会在彼此上化学吸附,从而屏蔽了底层表面。使用“切入吹扫”步骤来冲洗多余的DEATMS并重新暴露表面,效果更为完全的钝化。

Imec高级研究员Annelies Delabie在一次采访中表示,最近一次ASD研讨会的亮点之一是对潜在前驱体和抑制剂化学品之间相互作用的系统研究数量。Delabie强调,前驱体、抑制剂和工艺条件都必须协同工作才能达到预期效果。前驱体与抑制剂分子的反应程度甚至是去除抑制剂的能力决定了选择性、生长速率以及抑制剂需要补充的频率。

例如,阿贡国家实验室的主要材料科学家Angel Yanguas-Gil在MRS演讲中指出,过量前驱体气体的去除率通常低于吹扫气体的流速。前驱体与表面的相互作用对气流形成阻力。在ALD步骤之间不完全的吹扫会导致交叉污染和缺陷。他指出,除了在半导体制造中的应用外,ASD是研究表面反应性的优秀模型系统。在这里学到的经验也可以适用于传感器和催化剂等领域。

选择性蚀刻以获得更好的选择性和更多的工艺参数许多工艺方案还依赖选择性蚀刻来清除非生长区域的材料,无论是代替抑制剂的使用还是作为补充。在一篇综合评论中,格勒诺布尔阿尔卑斯大学的副教授Marceline Bonvalot及其同事详细说明了这种方案中蚀刻步骤必须满足的一些要求。首要任务当然是对生长区域和底层基材材料的高选择性,同时钝化非生长表面。蚀刻不应通过引入污染物或降低密度和粗糙度来损害生长区域中的目标薄膜。工艺工程师还需要记住,将蚀刻化学品引入沉积室会由于蚀刻化学品与沉积室壁的反应而带来交叉污染的风险。

速度慢,但仍然有用通过抑制剂沉积和选择性蚀刻步骤实现的复杂超级循环自然会导致产量损失。如果ALD速度慢,那么ASD则更慢。通常,选择性沉积所需的时间是ALD的两到三倍,才能达到相同的最终厚度。不过,如果这可以减少光刻步骤的数量,那也是值得的。

浮思特科技专注功率器件领域,为客户提供IGBT、IPM模块等功率器件以及MCU和触控芯片,是一家拥有核心技术的电子元器件供应商和解决方案商。