新闻资讯

新闻资讯 知识专栏

知识专栏这篇文章描述了一种多级图腾柱PFC拓扑,利用硅MOSFET的简单性和成熟性,以及一种新颖的模块化门驱动方法,达到与传统宽带隙半导体电路相当的效率,并具有更低的成本。

PFC拓扑的演变

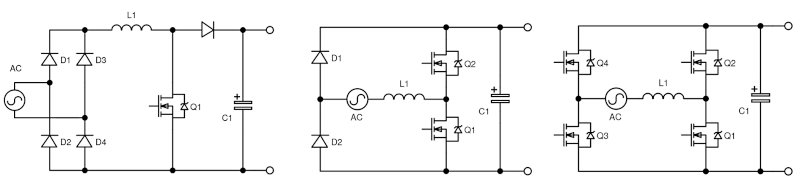

在更高功率水平上实现合规的实际方法是使用主动PWM电路,强制拉取的线电流接近正弦波。尽管转换阶段可以采取不同形式,但“升压”转换器是首选,因为它可以在低输入交流电压下工作,并生成一个稳压的高电压轨道,可以有效存储维持电力的能量。该“升压PFC”阶段最初采用线桥整流器和升压拓扑(图1左)。随着对更高效率的需求,例如在“能源之星80 plus”计划中,电路变得不可行,因为在任何一个时刻功率链中三台整流器的损耗太高,尤其是在低电压下。提出的解决方案是“无桥图腾柱PFC”(TPPFC)拓扑(图1中),将转换分为两个半波整流阶段。升压开关和由Q1和Q2组成的同步二极管在交流输入的不同极性下交替切换功能。D1和D2以电网频率导通,因此动态损耗微不足道,但可以用图1(右)中的同步整流器Q3和Q4替代,以实现导通损耗的增量改善。Q3和Q4被称为“慢”开关臂,而Q1和Q2为“快”开关臂,后者以高频率切换。控制较为复杂,专用控制器的选择有限,无论是模拟还是数字,但通过优化电感器和适当的热管理,可以实现良好的效果。

图1

根据器件选择,可以实现任意低的电压降和导通损耗,但对于快速开关的硅超结MOSFET,TTPFC电路在高频和高功率时证明不适用。这是因为该拓扑通常在高功率水平下以连续导通模式(CCM)运行,以控制可管理的峰值电流。然而,这导致了“硬”开关,其中Q1和Q2的体二极管被迫导通。当它们随后被正向偏置时,硅SJ-MOSFET的高回收能量在高开关频率下造成过度损耗,而若为了补偿而将频率保持在低位,电感器的尺寸和成本又不可接受。

宽带隙开关承诺解决方案,但……

宽带隙(WBG)半导体被誉为解决这一问题的答案,SIC具有低反向恢复电荷(Qrr),而GaN几乎没有。然而,这些器件确实存在缺点,特别是与Si-MOSFET相比的单位成本。SiC体二极管快速但仍有恢复电荷,并且前向电压降高达约3V。SiC MOSFET仍可能存在阈值不稳定性问题,这需要在制造过程中进行筛选,增加了一定成本,并且门驱动需要约18V以实现完全增强,通常接近绝对最大评级。GaN器件的门阈值更低,因此更容易受到噪声影响,且其绝对最大门电压仅约7V。门驱动至关重要,由于没有门氧化层,当超过阈值时,门电流会流动,必须加以控制。GaN HEMT单元也没有雪崩特性,因此过电压意味着瞬时故障。

SiC和GaN都具有令人印象深刻的开关速度,但在实际电路中,这使得PCB布局极为关键,边沿速率必须减缓,以避免难以控制的EMI和由寄生电感造成的有害电压过冲。因此,在TPPFC应用中,使用WBG器件的开关频率通常低于100kHz,不仅为了降低动态损耗和提高效率,还为了将基频设定在CISPR22/32导体EMI排放限制线的150kHz下限之下。由于它们的缺点,以及缺乏与WBG器件MHz开关所带来的小电感尺寸的优势,其吸引力有所下降,进一步加剧了包装标准化的缺乏。

更好的多级方法

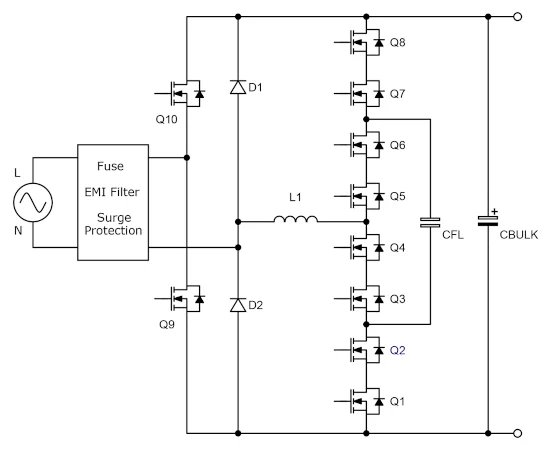

有一种替代方案——效率与WBG解决方案相当,但成本更低,并使用标准硅MOSFET——多级TTPFC(图2)。

图2

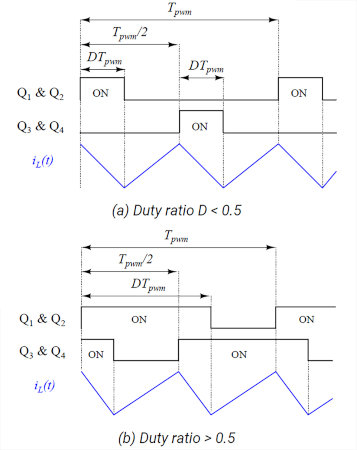

在该拓扑中,两个快速FET被两组四个串联硅MOSFET替代,每个仅需额定150V即可实现400V DC输出总线,允许使用具有非常低导通电阻和二极管反向恢复电荷的多源器件,从而实现与WBG解决方案相当的整体损耗。可以使用两组两个MOSFET,但这需要每个器件额定300V,而这种规格并不常见,因此采用两个串联连接的MOSFET(例如Q1和Q2)形成复合器件,共同驱动开关。开关腿中的开关被分为两组:Q1、Q2、Q7、Q8与Q3、Q4、Q5、Q6,每组以反相方式驱动。当Q1和Q2导通时,Q7和Q8关闭,反之亦然。类似地,Q5和Q6的驱动信号是Q3和Q4驱动信号的反相版本。对MOSFET Q3和Q4(同样适用于Q5和Q6)的驱动信号时序是对Q1和Q2(同样适用于Q7和Q8)驱动信号延迟半个开关周期的版本。通过对MOSFET组的相位移调制,采用不同的占空比同时实现输入电流和输出总线电压的调节,例如,在Q1/Q2和Q3/Q4之间(图3)。

图3

电感电流图显示了多级方法的一个主要优势——与传统TPPFC相比,电感看到了双倍的频率和一半的电压,或者说是四分之一的电压秒,这使得电感的尺寸减少到约四分之一,随之而来的成本和重量也得以降低。通常可以使用低成本的“SendustTM”核心。由于较低的电压秒乘积,差模EMI也减少,进一步降低了EMI滤波器的尺寸和成本。

“飞行”电容器CFL在Q2/3和Q6/7连接点之间维持一半的总线电压,如有必要,还可以通过两个额外的电容器和钳位二极管确保串联对的电压平衡,这在正常操作中不会消耗电力。二极管D1和D2在启动时将CBULK涌流电流偏离电感,以避免磁饱和,导致高初始开关电流。

优化功率半导体和驱动

八个硅MOSFET和隔离门驱动可能看起来很复杂,但耗散功率分散在各个器件上,因此它们可以小型化并表面贴装。例如,在一个3kW设计中,它们每个可能仅耗散2.5W,因此通常可以采用小型的5mm x 6mm “SuperSO-8”封装,并利用PCB焊盘作为散热器。在一个两级WBG实现中,热量集中在两个器件的热点上,可能需要使用引脚封装,例如TO-247,增加了额外的组装成本和可靠性问题。

传统上,门驱动的选择包括笨重且昂贵的主动电路,这些电路需要光隔离器进行隔离,并且需要隔离电源轨,通常是双极的。在某些方案中,脉冲变压器可以替代光隔离器,但为了最佳性能,这些通常会后续连接有源驱动阶段。一个显着减少体积、成本和复杂性的解决方案是ICERGi的IC70001器件,封装在一个小型2mm x 2mm U-DFN2020-6中。该驱动器从内部单稳态电路生成最佳的门驱动波形,具有精确的传播延迟,通过外部变压器的短脉冲触发开关。脉冲的持续时间通常仅为100ns,因此变压器可以小型化且绕组圈数较少。它们可以方便地作为平面类型实现于转换器PCB上,ICERGi可以为使用4 x 7mm铁氧体核心的合适设计提供布局。实际上只需四个变压器,因为MOSFET是成对驱动的。每对MOSFET的门驱动仍然必须相互隔离,但这可以通过一个单一变压器的独立绕组实现,绕组可以位于E型核心的每个外侧,以实现所需的隔离爬电和间隙。变压器的小尺寸和构造还提供了低隔离电容,这是良好的DV/dt免疫力所必需的。

优化控制

实现最高效率和可靠性取决于多级TPPFC阶段的控制,而在没有专用IC的情况下,ICERGi开发了专有固件,以在标准ARM Cortex-M0微控制器上运行,计算负载最小,同时结合一些指定的外部逻辑,执行所有必要的功能:功率因数校正、输出总线电压调节和所有必要的参数感应及保护功能。例如,除了支持“智能”过载、过电压和过温度监测外,固件在启动和瞬态条件下直接控制飞行电容器电压,从而确保MOSFET之间的电压平衡,不会超过它们的额定值。使用现成的微控制器提供了供应安全性,还可以根据需要添加额外功能,例如驱动“慢”腿同步MOSFET门或通过通信接口控制和监测。

性能基准

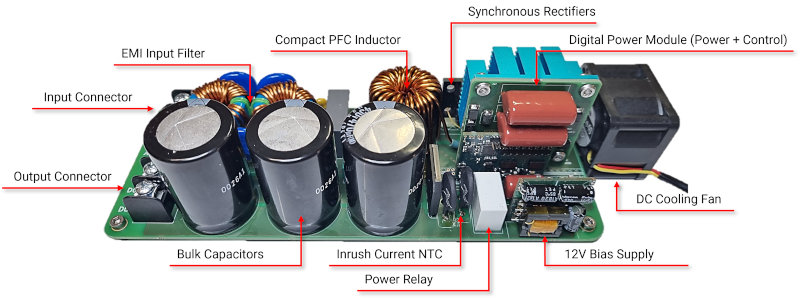

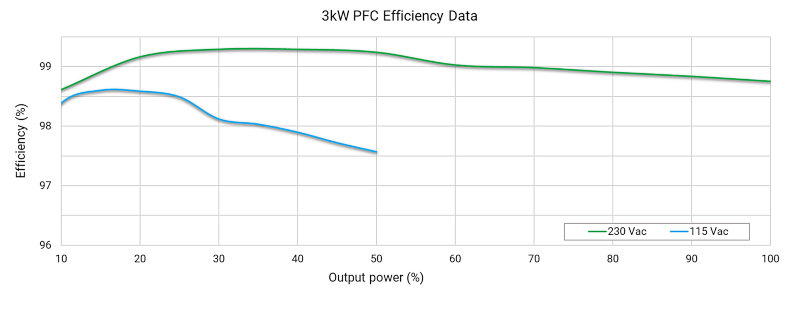

ICERGi在参考设计和演示板中展示了多级TPPFC方法及其门驱动和控制固件的有效性。例如,一款额定为3kW,输入范围为85 VAC到265 VAC的版本,完整功能单元的功率密度约为100/in³,包括EMI滤波和辅助电源(图4)。该单元的效率峰值约为99.3%(图5),同时符合IEC/EN 61000-3-2线电流谐波和EN 55022/32导体排放限值,具有10dB的裕量。

图4

图5

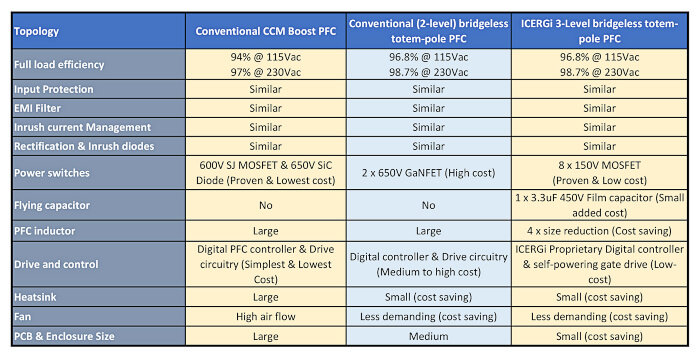

作为所述设计方法优势的总结,表1对比了使用Si SJ-MOSFET加SiC二极管的传统方法、两级GaN解决方案和多级ICERGi解决方案的属性。也许最具说服力的比较是BOM成本——ICERGi的分析显示,相比于GaN节省33%,相比SiC节省25%,在相似效率下,包括ICERGi固件的许可费用。

表1

ICERGi还将控制器与其支持组件和门驱动封装成各种“可插拔”模块,可以用于客户设计中技术的评估。

结论

采用硅MOSFET的多级TPPFC方法可以与WBG解决方案一样高效,但成本更低,无需交错设计以达到至少3kW的功率。使用低压现成的硅MOSFET消除了对昂贵、单一来源WBG器件的担忧,而ICERGi的自供电驱动器提供了优雅且低成本的解决方案。许可ICERGi的固件使设计者能够使用商品ARM处理器作为控制器,消除了对单一来源专用IC的依赖——在组件分配和供应中断的时代,这一点尤为重要。此外,参考设计使得设计集成变得简单,降低了研发过程中的风险,加快了最终产品的上市时间。

浮思特科技专注功率器件领域,为客户提供IGBT、IPM模块等功率器件以及MCU和触控芯片,是一家拥有核心技术的电子元器件供应商和解决方案商。