新闻资讯

新闻资讯 知识专栏

知识专栏场效应晶体管(FET)在设计为400V-500V母线电压的逆变器中具有吸引力,相比于硅绝缘栅双极晶体管(IGBT)或宽禁带(WBG)替代品,它们提供了更优的导通损耗和开关损耗。除了低损耗之外,电动机驱动逆变器中的功率开关还必须具备短路保护,以便检测并安全关断,避免系统的灾难性故障。这些6mΩ/750V的SIC FET提供了5微秒的可用短路耐受时间。本文将讨论这一特性的必要性,以及为什么这些第四代SiC FET在满足这一需求时不妥协于RDS(on)。

引言

碳化硅(SiC)FET已经在许多应用中站稳了脚跟,包括电动车(EV)的车载和非车载充电、数据中心电源、太阳能逆变器等。预计碳化硅FET最大的增长领域将是在电动车牵引逆变器中,这将提供更长的续航里程、更低的电池成本和更高的功率密度。SiC FET已在400V电池系统中推出, 在更高的母线电压(500V或800V)下,其应用案例甚至更具吸引力。这些系统中的驱动系统逆变器通常是3相、2级电压源逆变器,工作频率低于20kHz。在此应用中,开关在整个负载范围内提供低导通损耗和开关损耗至关重要。SiC FET是很好的候选者,因为它们不存在膝压(改善轻负载效率),且导通和开关损耗低。然而,直到现在,碳化硅开关选项在短路韧性方面尚未满足应用需求。本文将讨论为什么UnitedSiC/Qorvo的第四代堆叠SiC FET是一个理想的候选者,在保持低导通电阻的同时,为设计人员提供可用的(最多5微秒)短路耐受时间。

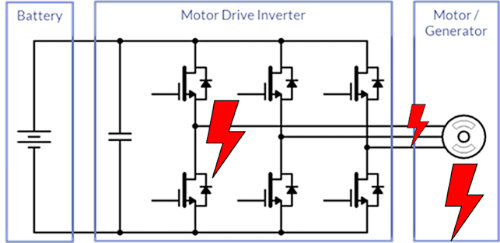

短路韧性对于电动机驱动逆变器中的功率半导体开关尤为重要,要求具备某种故障防护能力,允许系统检测并安全关闭,避免灾难性系统故障。图1展示了在电动机驱动逆变器系统中常见的各种短路故障。当逆变器相腿发生穿透故障时,系统可能会经历直流母线的直接短路。如果相腿中的一个开关短路故障,而另一个开关的栅极驱动仍然有效,就会发生这种情况。或者,如果一个错误信号从栅极驱动器施加到相腿FET之一,穿透故障也可能发生。当电动机绕组绝缘失效时,相腿之间可能会发生短路。最后,相到地的故障可能发生在电动机绕组绝缘失效的情况下,从而造成与电动机外壳的短路。在这些故障模式中,功率半导体开关必须承受整个直流母线电压的直接短路,或与相腿中的互补开关共同承受短路母线电压。在这些严酷条件下,功率半导体元件通常会在微秒内发生灾难性失效,使整个系统无法操作。

图1

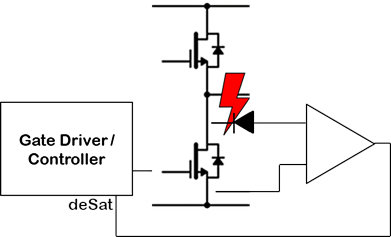

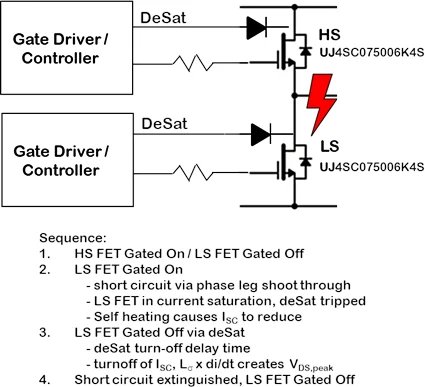

已经提出了多种检测短路的方法,但大多数都基于电流测量或开关的去饱和(de-saturation, deSat)检测(即漏极到源极电压或IGBT的集电极-发射极电压)。图2展示了相腿低侧开关的标准deSat方法。使用快速高压的deSat二极管,仅在开关导通期间进行监测。如果在开关导通时,开关上的电压高于预期,则会触发一个阈值(通常为7-9V),指示过电流或短路事件。deSat信号的状态用于关闭栅极驱动器输出,开关在灾难性失效之前被关断。然而,必须注意防止deSat信号的误触发。采用一个消隐时间来过滤从开关开启到达到其标称漏极-源极电压的时间。此外,避免多余的deSat误触发通常包括对输入进行滤波(RC等),以避免噪声引起的触发,这可能进一步增加实际最小检测时间。因此,在噪声免疫性与短路检测和关断时间之间存在权衡。设计人员发现这些约束在没有几微秒的假设续航能力的系统中难以实施。迄今为止,广带隙器件因其低导通电阻和较小的芯片尺寸,相比于其牵引IGBT对手的表现不佳,后者历来提供超过10微秒的短路续航能力。然而,随着硅IGBT不断降低Vce(on)和开关损耗,加上改进的栅驱动器,短路续航能力的评级已降至10微秒以下。

图2

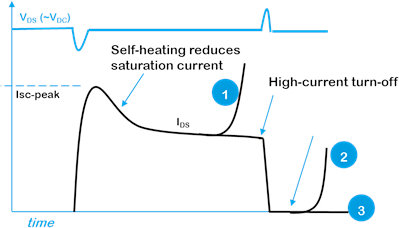

与功率半导体开关相关的一些特性影响其处理短路故障的能力。为了理解这些特性,我们可以首先查看图3中显示的FET在短路条件下所经历的典型失效机制。在图中,表示了一种类型1短路的典型I-V特性,母线电压施加在器件上。在高di/dt部分,功率环路杂散电感的电压下降导致在恒定电压上出现小的跌落/过冲。在图中,器件的短路电流(黑色曲线)快速增加,因为FET在导通状态下的阻抗较低。在此阶段,器件的结温因瞬时功率过高而快速升高。随着结温和电流的上升,FET最终达到电流饱和状态,限制了峰值短路电流(Isc-peak)。高瞬时功率的耗散继续加热FET,短路电流因自热效应和饱和电流的下降而开始降低。

图3

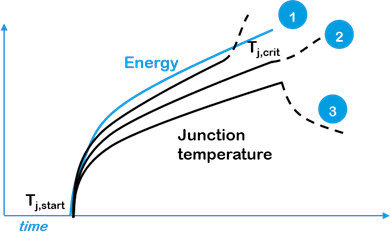

如果在栅极驱动器关闭FET通道之前,器件的结温达到热不稳定水平,就可能发生失控事件,如图3中的bubble1所示。在传统的SiC MOSFET中,如果在高电场和高结温下栅极氧化层破裂,也可能发生在关断之前的失效。图中所示的失效模式2表示FET关断后的热失控。在此模式下,器件在高温下的漏电流(可超过600°C)可能导致热失控,或锁定器件内部的寄生晶体管,造成灾难性失效。最后,在模式3中,器件能够安全关断短路故障,器件的结温缓慢回到其标称运行温度。在高压工作条件下的先进SiC FET,其短路时间可视为一个绝热过程。碳化硅的3-6倍较小芯片尺寸及其相关的热容量降低,导致在相同短路能量下的温度上升大于其硅基对手。

SiC FET提供突破性性能

根据图3的讨论,最佳的功率开关是能够减少Isc-peak而不牺牲导通电阻,从而保持短路能量低、降低温升并避免热失控的开关。该开关还应避免诸如栅氧化层破裂等次级失效模式,并避免任何寄生双极晶体管的锁定。虽然高温下的p-n结漏电流是不可避免的,但最佳开关应在温度变化中保持足够高的阈值电压,以降低增加热失控的通道漏电流分量。

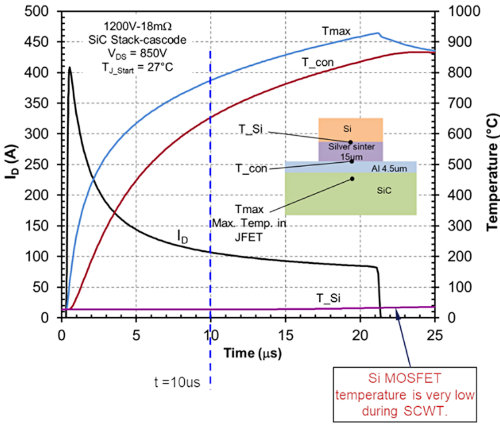

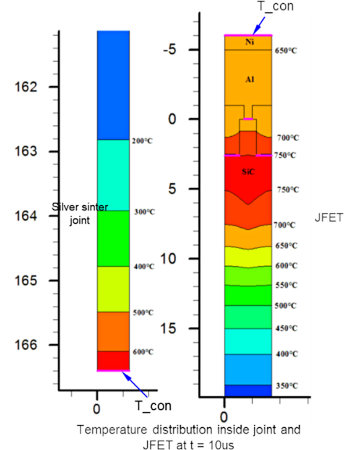

这些特性在垂直SiC JFET中均有体现。SiC JFET在650V至2000V以上的技术中,提供最低的单位导通电阻,同时也提供良好的电流饱和。垂直JFET器件结构在其主要漏电路径(漏极-栅极)中没有内部寄生晶体管。在器件结构中没有栅氧化层,且阈值电压与温度的关系相比于Si或SiC MOSFET更加平坦。当与低电压Si MOSFET结合使用时,常闭式堆叠SiC FET在导通电阻与短路韧性之间提供了优越的权衡。同时,还可以证明,在短路故障期间(长达10微秒),热量集中在SiC JFET中,而堆叠的低电压Si MOSFET则不会出现显著的温升。图4展示了在短路条件下SiC堆叠FET的电热TCAD仿真。在10微秒内,温升(可超过700°C)主要集中在SiC JFET的本体和顶部金属化层中。此时,Si MOSFET则保持在其最大结温以下。因此,SiC JFET决定了SiC堆叠FET的短路能力。

图4

UnitedSiC(现为Qorvo)利用其第四代SiC FET开发了这些特性。新推出的UJ4SC075006K4S产品在标准分立封装中拥有行业最低的6mΩ导通电阻。该器件的电压额定值为750V,为400V或500V母线应用提供了充足的设计余量。超低的导通电阻(不到其最近竞争对手的一半)在提供用户习惯于UnitedSiC FET的所有附加优点的同时实现,如便捷的0-12V或0-15V栅极驱动,出色的整流二极管,以及由较低器件电容(Coss)带来的低开关损耗。

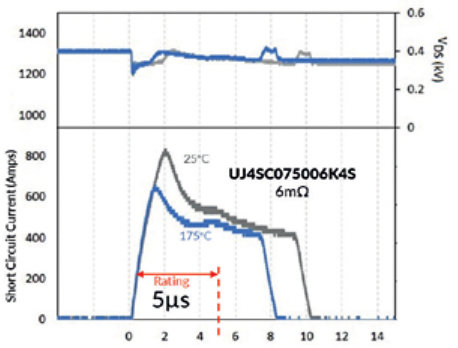

对于SiC功率开关而言,首次实现了坚固的短路性能,而无需牺牲成本或效率。这些750V额定的SiC JFET的特定导通电阻不到其650V SiC MOSFET竞争对手的1/3。UJ4SC075006K4S 750V/6mΩ SiC FET也设计了超过5微秒的可用短路耐受时间。图5显示了在400V母线电压下,典型UJ4SC075006K4S SiC FET的类型1短路特性。当起始结温为25°C时,该器件在10微秒的短路后安全关断,即使从器件的Tj,max=175°C起始,也能通过8微秒的短路测试。器件在5-10倍标称的电流饱和(在Tj,start=25°C时为800A,在Tj,start=175°C时为600A),足以应对过电流浪涌事件,同时又低到足以实现安全的短路耐受时间。

图5

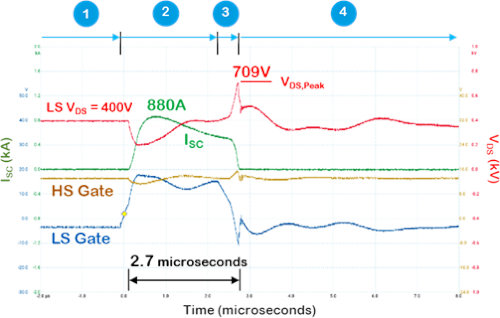

UJ4SC075006K4S可以在提供deSat保护的商用栅极驱动器下安全关断。在图6中,我们展示了UJ4SC075006K4S在两个开关位置的相腿短路。使用Analog Devices的商用(ADuM4136)栅极驱动器进行短路检测和安全关断,当低侧开关的VDS超过deSat阈值(9.2V)并在312ns的消隐时间后发生。在测试中,短路电流峰值达到880A,随后因器件的自热效应,故障电流在关断前降低到约500A。deSat保护在2.7微秒内安全关断短路,远低于UJ4SC075006K4S的短路耐受时间评级5微秒。

结论

UnitedSiC(现为Qorvo)最近推出了行业最低导通电阻的750V、6mΩ SiC FET,利用其第四代技术实现了突破性性能。得益于其内部SiC JFET提供的优越韧性,这款新FET为设计人员提供了可用的5微秒短路耐受时间,即使在高温下,也无需牺牲导通电阻。新款UJ4SC075006K4S使设计人员能够使用在标准驱动器中找到的deSat保护,非常适合于400V或500V母线应用。

浮思特科技专注功率器件领域,为客户提供igbt、IPM模块等功率器件以及MCU和触控芯片,是一家拥有核心技术的电子元器件供应商和解决方案商。