新闻资讯

新闻资讯 知识专栏

知识专栏在嵌入式系统中,许多应用常常使用离散逻辑器件,例如74'HC系列。这些逻辑器件的优点在于它们可以独立于微控制器(MCU)工作,并且响应速度比软件快得多。然而,这些器件会增加材料清单(BOM),并且需要额外的PCB面积。

为了解决这个问题,许多微芯科技的微控制器在PIC MCU上集成了一种名为可配置逻辑单元(Configurable Logic Cell, CLC)的外设,或在AVR MCU上集成了一种类似的外设,称为可配置自定义逻辑(Configurable Custom Logic, CCL)。这两种外设都实现了软件定义的自定义逻辑,可以独立于CPU执行。换句话说,一旦自定义逻辑功能设置完成,其行为就不再依赖于微控制器。

这些外设为开发简单的逻辑电路、混合信号以及与其他硬件外设集成提供了有用的工具。但这些外设的一个局限性是每个实例的逻辑量非常小。每个CLC大约相当于一个查找表(LUT),而CCL则是一个内部有几个独立LUT的实例。

引入可配置逻辑块

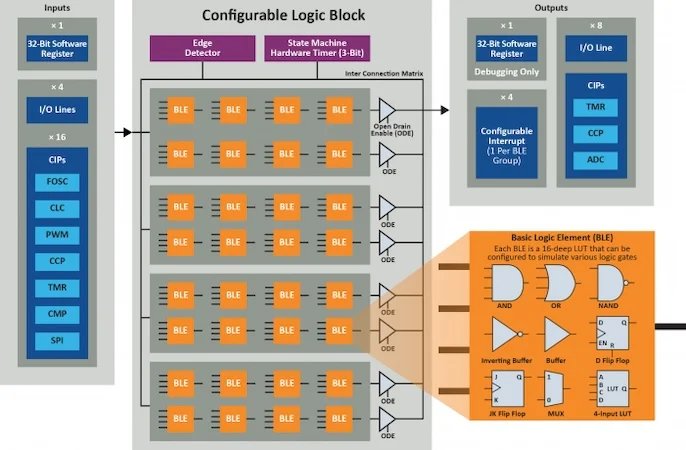

为了支持更复杂的应用,开发了一种新型逻辑外设——可配置逻辑块(Configurable Logic Block, CLB),如图1所示。它首次出现在PIC16F13145系列微控制器中。

图1

需要注意的是,CLB并不一定取代CLC或CCL外设。微控制器可以同时拥有CLC/CCL和CLB。

PIC16F13145系列的CLB由四组逻辑组组成,每组包含八个基本逻辑单元(BaSIC Logic Element, BLE)。各逻辑组之间是相互连接的,每个逻辑组代表两个GPIO输出和一个可选的CPU中断。

CLB中的其他元素包括:

一个具有解码输出的专用3位硬件定时器

输入信号的边沿检测器

一个用于调试的32位输出寄存器

此外,微控制器上的其他核心独立外设输出可以用作CLB的输入,以实现更复杂的设计。

CLB从微控制器的内存中初始化,并能够通过外设引脚选择(Peripheral Pin Select, PPS)直接控制引脚。PPS允许用户重新分配与硬件外设使用的I/O引脚,以获得更大的设计灵活性。例如,如果RA1用于SPI时钟而RA6更为合适,则可以通过PPS重新映射该引脚。

所有BLE在整个电路中共享一个通用时钟,其源在软件中配置,并可选配一个时钟分频器。CLB可以使用来自微控制器的内部时钟源或外部提供的源。当在5.5V下运行时,BLE的典型传播时间小于6纳秒。

CLB合成

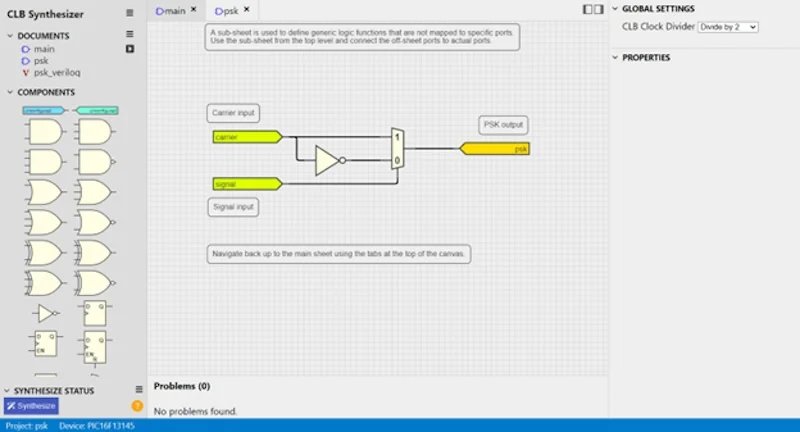

由于CLB的复杂性远高于CLC或CCL,开发了一种名为CLB合成器的工具。CLB合成器提供了一个图形界面来配置逻辑,如图2所示。

图2

除了逻辑原语,合成器还支持更高级逻辑块的库,这些库可以是预先提供的或由用户自定义构建的。

在与图形工具交互时,会在后台生成一个用于合成的Verilog模块。如果开发人员希望编写自己的Verilog或已有文件,可以将该文件直接作为模块导入到工具中。

CLB合成器的输出是一个包含设置CLB的位流的汇编文件,以及一些用于将CLB配置为外设的源代码。该工具可以通过MPLAB代码配置器(MCC)或独立的在线工具运行。MCC是一个代码生成工具,允许用户使用可视化界面设置和配置微控制器中的外设。在配置硬件外设后,MCC生成初始化代码和设备API。

在运行时,CLB位流直接从程序内存中加载,使用板载硬件。这种实施方式使程序能够在运行时更改CLB的配置。加载过程可以重复进行,使用存储在设备内存中的不同位流。

使用CLB的设计示例

为了演示CLB的应用,我们将讨论两个示例:

七段显示器转换器

SPI到WS2812串行数据转换器

这些用例示例是可以复制并用作完整解决方案的一部分的构建模块,旨在展示CLB在设计中的实用性。

七段显示器转换器

七段显示器可以由常规的I/O引脚驱动。标准实现通常需要一个软件定义的查找表,将输入数字转换为显示器的正确输出模式。

在这个实现中,CLB作为硬件查找表工作。所需的输出字符(0到F)从软件加载到CLB输入寄存器中。显示器的每个输出段由一个LUT控制,该LUT将输入映射到输出。

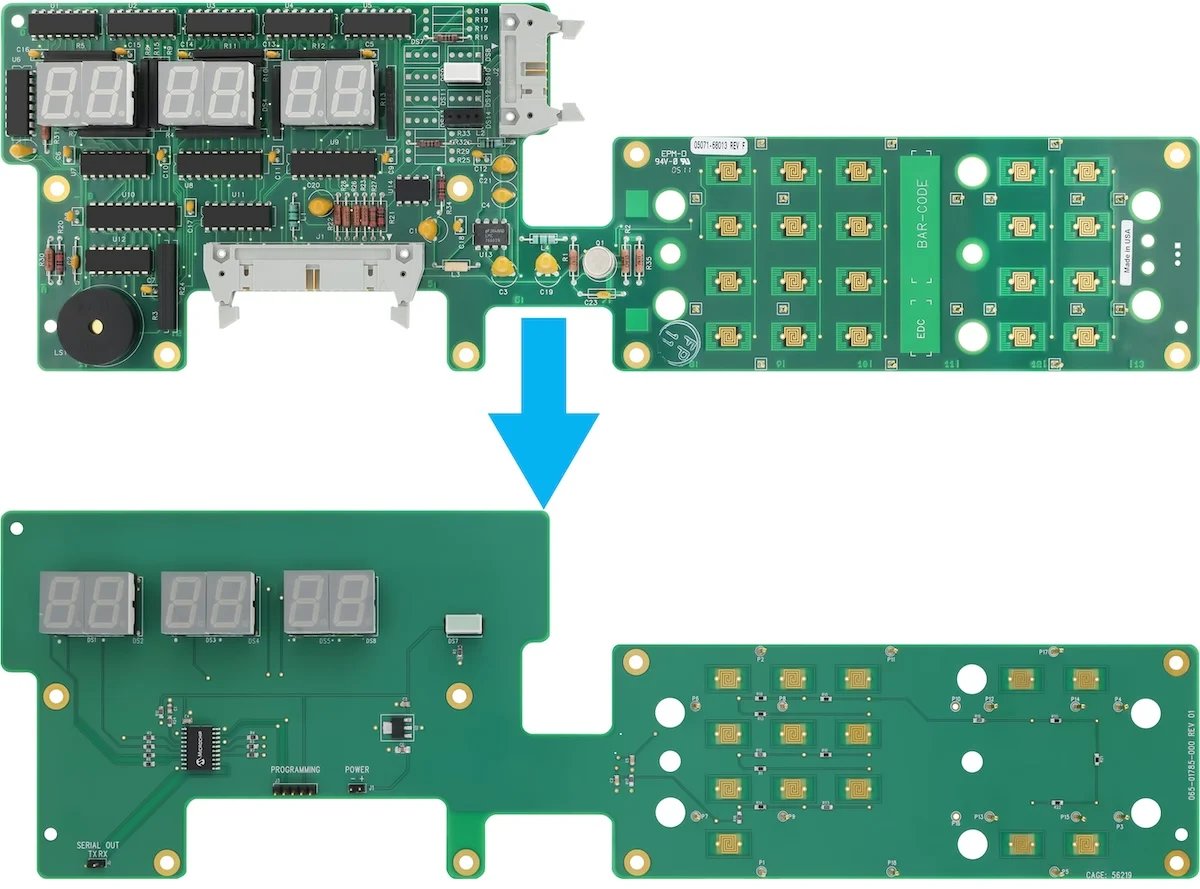

这一用例示例曾在内部用于构建一个新的计时系统控制板。原始用户界面是在1980年代使用74'HC系列逻辑开发的。通过使用CLB升级设计,单个20引脚的微控制器可以实现显示和键盘逻辑。

如图3所示,这大大减少了材料清单(BOM)。顶部的原始电路板比底部的新设计包含更多组件,后者使用了带有CLB的MCU。

图3

SPI到WS2812串行数据转换器

WS2812是一种用于控制LED阵列的1线串行协议,采用脉宽调制。在这种情况下,SPI硬件被用作要发送到LED的数据的移位寄存器,而CLB将SCLK和SDO转换为预期的输出。

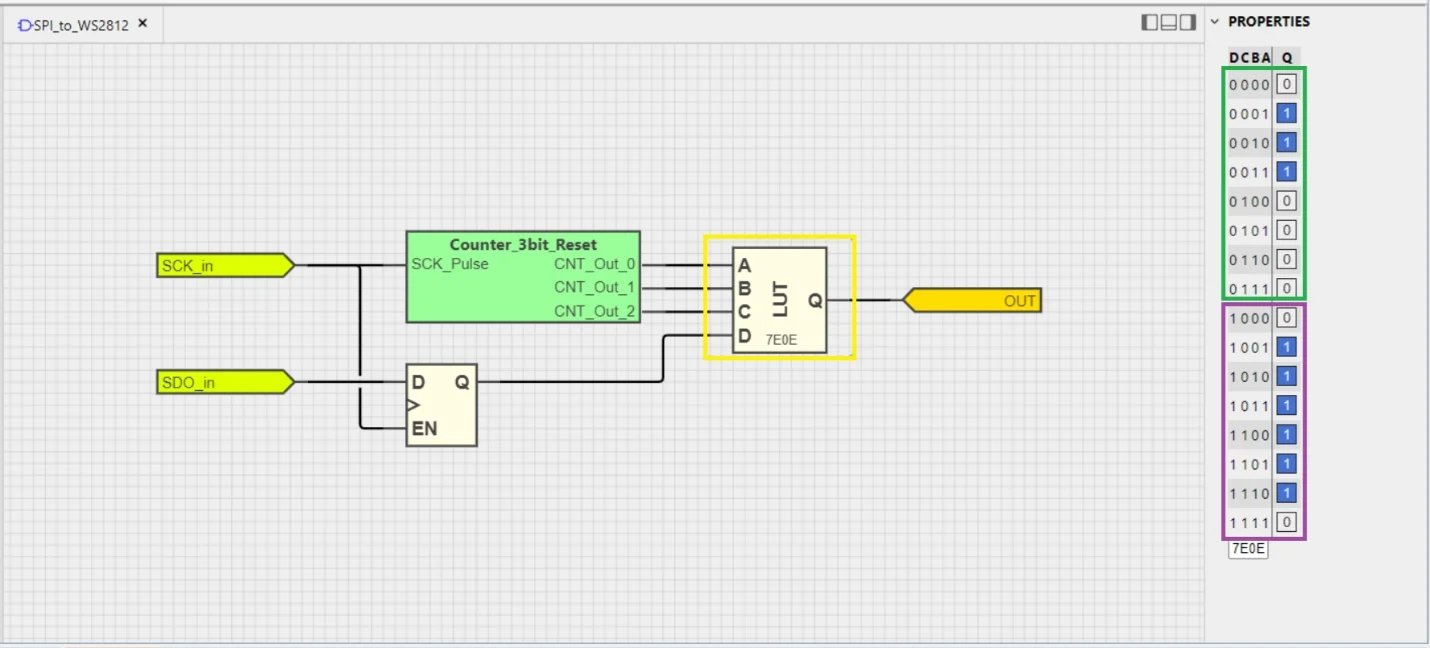

如图4所示,这一实现使用了一个单触发的3位计数器、一个带使能的D触发器和一个4输入的LUT。

图4

这一实现的关键在于SPI和CLB的时钟源。SPI时钟设置为空闲高电平,在上升沿变换状态,并以800 kHz的WS2812输出频率运行。CLB的8 MHz时钟源是10倍更快的。

当SCLK为低时,3位计数器被触发并开始计数。当计数器达到7(0b111)时,它停止并保持在0,直到下一个时钟脉冲的低周期。

计数器的输出与锁存版本的输出数据一起馈入4输入的LUT。这设置了数据的输出模式,如图4右侧所示。在计数器重置后,计数器输出将保持在0以完成周期。然后,如果需要,SPI硬件中的下一个字节将被传输,重复这一周期。

可配置逻辑块的优点

这两个示例展示了微控制器内部离散逻辑的优势。硬件外设将任务卸载给CPU,从而改善响应时间和功耗,同时减少部件数量。CLB使得开发以前无法在微控制器内部实现的复杂应用成为可能。目前,CLB可以在PIC16F13145系列微控制器上找到,用户可以通过Microchip Direct或其他电子分销商直接获取。

浮思特科技专注功率器件领域,为客户提供IGBT、IPM模块等功率器件以及MCU和触控芯片,是一家拥有核心技术的电子元器件供应商和解决方案商。